Description and Features#

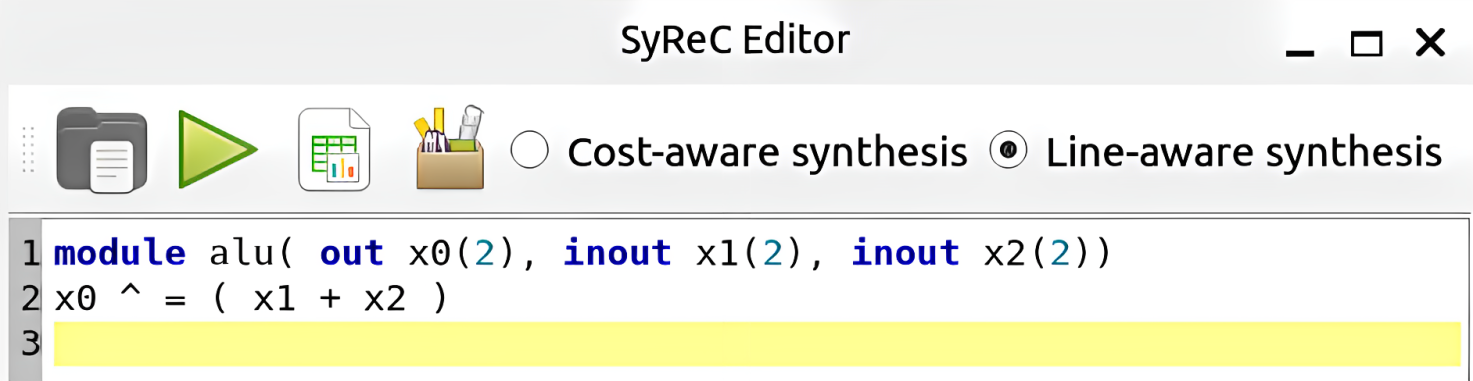

The SyReC Synthesizer [1] allows users to automatically synthesize reversible circuits from a high-level HDL description. The proposed tool accepts any HDL description following the SyReC grammar and syntax as described in detail in [2] (example circuits are available in the test/circuits directory). The tool provides an easy-to-use GUI with which the user can specify any preferred functionality. As an example, consider the SyReC program for a simple 2-bit Adder as shown in the figure below.

This Adder computes the sum of the inputs x1 and x2 and stores the result in the output signal x0. By clicking on the button, the tool automatically synthesizes the corresponding circuit. To this end, two complementary synthesis schemes

are available:

1. Cost-aware synthesis: In this synthesis scheme, additional circuit lines (representing circuit signals) are introduced to store the corresponding intermediate results of each operation—thereby providing the liberty to accordingly modify the circuit without having any effect on the original inputs (for more details, refer [3] and [2]). This results in a circuit description where the gate costs are kept moderate at the expense of a substantially larger number of additionally needed circuit lines. The following figure depicts the circuit which results when synthesizing the program from above.

2. Line-aware synthesis: This synthesis scheme aims to the keep the number of additional circuit lines as small as possible. To achieve this, the corresponding intermediate results of each operation are computed and stored using one of the available circuit lines (rather than additional circuit lines). Afterwards, the inputs are re-computed with the help of the corresponding inverse operations (for more details, refer [4]). The figure below depicts the circuit which results when synthesizing the program from above using the line-aware scheme.

Furthermore, the tool allows to simulate the resulting circuit (By clicking on the  button) as well as to determine the its gate costs (By clicking on the

button) as well as to determine the its gate costs (By clicking on the button).